aprile

Classification based on different parameters:

Semiconductor Silicon Wafer is the basis for manufacturing silicon semiconductor products

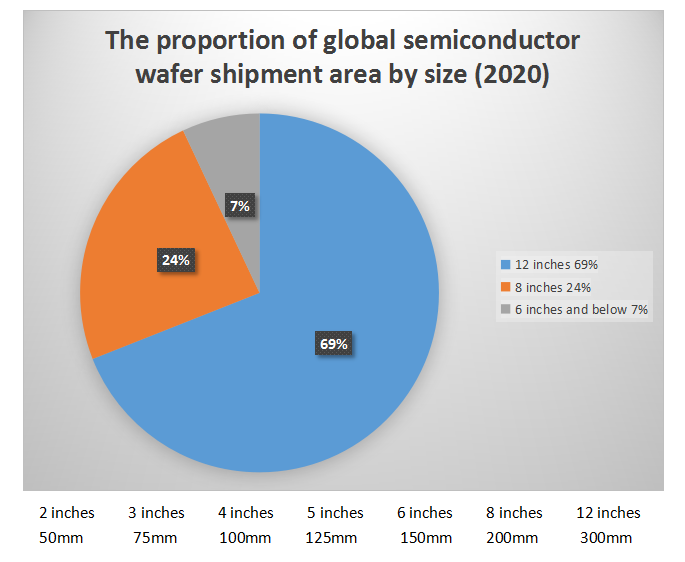

aprile (aprile), aprile 2 pollici (50mm), 3 pollici (75mm), 4 pollici (100mm), 5 pollici (125mm), 6 pollici (150mm), 8 pollici (200mm), 12 pollici Pollici (300mm), sotto l'influenza della legge di Moore, i wafer di silicio semiconduttore si sviluppano costantemente nella direzione di grandi dimensioni. Attualmente, 8 pollici e 12 pollici sono prodotti tradizionali, rappresentando più di 90% della superficie totale di spedizione.

Classified according to doping level:

Secondo il grado di doping, i wafer di silicio semiconduttore possono essere divisi in leggermente drogati e fortemente drogati.

- I wafer di silicio fortemente drogati hanno una grande quantità di elementi droganti e una bassa resistività, e sono generalmente utilizzati in dispositivi di alimentazione e altri prodotti;

- I wafer di silicio drogati con luce hanno una bassa concentrazione di drogaggio e sono generalmente utilizzati nel campo dei circuiti integrati, con maggiori difficoltà tecniche e requisiti di qualità del prodotto.

Poiché i circuiti integrati rappresentano più di 80% del mercato globale dei semiconduttori, c'è una maggiore domanda globale di wafer di silicio leggermente drogati.

Classification according to process:

Secondo il processo, i wafer di silicio semiconduttore possono essere suddivisi in wafer di macinazione, cialde di lucidatura, wafer epitassiali di wafer speciali a base di wafer di lucidatura, COSÌ IO, eccetera.

- I fogli abrasivi possono essere utilizzati per produrre dispositivi discreti;

- I fogli di lucidatura leggermente drogati possono essere utilizzati per produrre circuiti integrati su larga scala o come materiali di substrato per wafer epitassiali, e fogli di lucidatura fortemente drogati sono generalmente usati come materiali di substrato per wafer epitassiali.

- Rispetto ai fogli abrasivi, i fogli di lucidatura hanno una migliore planarità e pulizia della superficie.

- Sulla base di wafer levigati, wafer ricotti, wafer epitassiali, SOI wafers and junction isolation wafers can be fabricated.Annealing wafers High temperature heat treatment of polished wafers in a hydrogen or argon atmosphere to remove oxygen near the wafer surface can improve the integrity of the surface crystals.

- Il wafer epitassiale è uno strato di silicio monocristallino cresciuto a vapore formato sulla superficie del wafer lucidato, in grado di soddisfare le esigenze di strutture multistrato che richiedono integrità cristallina o diversa resistività.

- Wafer di silicio SOI (Silicio su isolante) è uno strato di pellicola di ossido ad alto isolamento elettrico inserito tra due wafer levigati, che può raggiungere un'elevata integrazione, basso consumo energetico, alta velocità e alta affidabilità del dispositivo, e può essere utilizzato anche sulla superficie dello strato attivo.

Si forma uno strato di diffusione di arsenico o arsenico. I wafer di silicio per l'isolamento delle giunzioni si basano sui progetti dei clienti, utilizzando l'esposizione, tecniche di impiantazione ionica e di diffusione termica per preformare uno strato incorporato di IC sulla superficie del wafer, e quindi far crescere uno strato epitassiale sopra.

Classification according to application scenarios:

Secondo diversi scenari applicativi, I wafer di silicio semiconduttore possono essere suddivisi in Prime Wafer e Dummy Wafer.

- Prime Wafer è utilizzato nella fabbricazione di prodotti a semiconduttore, e Dummy Wafer viene utilizzato per riscaldarsi, riempire i posti vacanti, e testare lo stato del processo delle apparecchiature di produzione o la qualità di un processo.

- I wafer fittizi sono generalmente tagliati dalle parti di scarsa qualità su entrambi i lati della bacchetta di cristallo. A causa dell'enorme quantità di utilizzo, alcuni prodotti saranno riciclati e riutilizzati se le condizioni sono soddisfatte.

- I wafer di silicio riciclato sono chiamati Reclaimed Wafer. Secondo i dati di Guanyan.com, la fonderia di wafer di processo a 65 nm deve aggiungere 6 wafer falsi per ogni 10 wafer positivi, e il processo a 28 nm e inferiore deve essere aggiunto 15-20 wafer falsi per ogni 10 wafer positivi.

https://www.youtube.com/watch?v=N57A-9mi-Mk

Contattaci per saperne di più !

e qui ci sono applicazioni più interessanti .